Vaddi, R., Dasgupta, S., Agarwal, R.: Device and circuit co-design robustness studies in the subthreshold logic for ultralow-power applications for 32 nm CMOS. In: 2010 IEEE 25th International Symposium on Defect and FaultTolerance in VLSI Systems, pp. Hariharan, A.N., Pontarelli, S., Ottavi, M., Lombardi, F.: Modeling open defects in nanometric scale CMOS. In: Custom Integrated Circuits Conference, 2008. Nassif, S.: Process variability at the 65 nm node and beyond. In: 2016 IEEE International Symposium on Circuits and Systems (ISCAS), pp.

Zimpeck, A.L., Meinhardt, C., Posser, G., Reis, R.: FinFET cells with different transistor sizing techniques against pvt variations. In: 2014 27th IEEE International System-on-Chip Conference (SOCC), pp. 1–6 (2015)įarkhani, H., Peiravi, A., Kargaard, J.M., Moradi, F.:Comparative study of finFETS versus 22 nm bulk CMOS technologies: SRAM design perspective. In: 4th International Conference on Reliability, Infocom Technologies and Optimization (ICRITO) (Trends and Future Directions), pp.

#Cmos schmitt trigger optimal layout full

1–6 (2018)Ībbas, Z., Olivieri, M., Khalid, U., Ripp, A., Pronath, M.: Optimal NBTI degradation and pvt variation resistant device sizing in a full adder cell. In: ANALOG 2018 16th GMM/ITG-Symposium, VDE, pp.

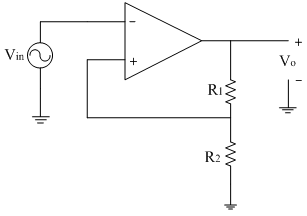

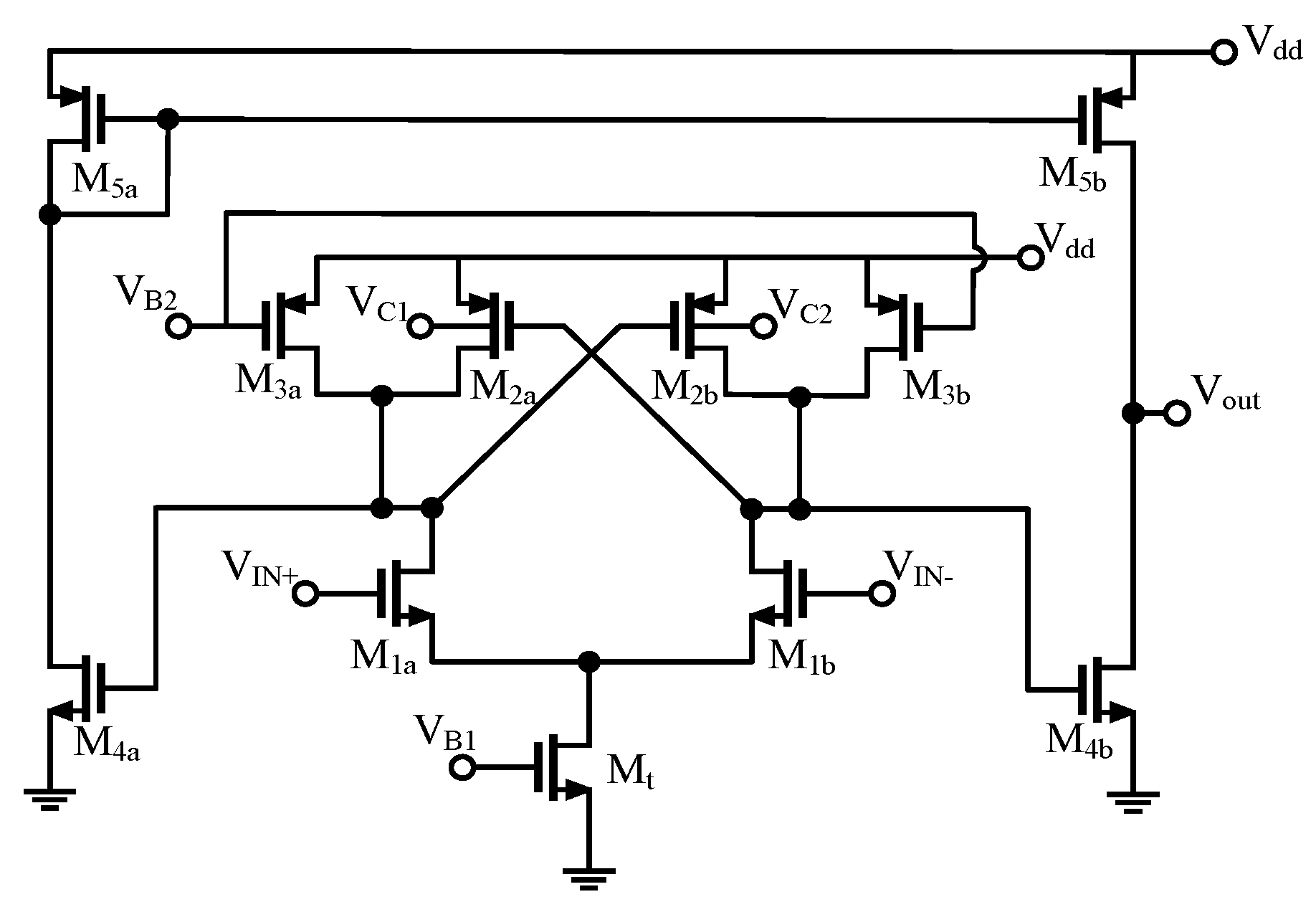

IEEE (2010)īleitner, A., Goeppert, J., Lotze, N., Keller, M., Manoli, Y.: Comparison and optimization of the minimum supply voltage of schmitt trigger gates versus CMOS gates under process variations. Manoli, Y.: Energy harvesting–from devices to systems. Miorandi, D., Sicari, S., De Pellegrini, F., Chlamtac, I.: Internet of things: vision, applications and research challenges. Exploring voltage and transistor sizing made possible a reduction of about 24.84% on power consumption. On average, scenarios with a lower supply voltage applied on layouts with a smaller number of fins, presented adequate robustness in high variability scenarios. Thus, the main contribution of this work is to identify the relationship between transistor sizing, supply voltage, energy, and process variability robustness to achieve a minimal energy consumption circuit while keeping robustness. Yet, Schmitt Trigger operation at nominal voltage still introduces high deviation on power consumption. Schmitt Trigger inverters are frequently used for noise immunity enhancement, and have been recently applied to mitigate radiation effects and variability impact. Given the broad set of IoT devices running on battery-oriented environments, energy consumption should be minimal and the operation reliable.

The IoT development alongside with the more pronounced impact of process variability in modern technology nodes, is the central reason to control variability impact.

0 kommentar(er)

0 kommentar(er)